Design & Test impedanzkontrollierter Leiterplatten · Software & Testsysteme zur Fehlerdiagnose auf Leiterplatten

Speedstack Multilayer Leiterplatten-

Lagenaufbausoftware

Speedstack Multilayer-Lagenaufbauprogramm

<

>

Speedstack Materialbibliothek

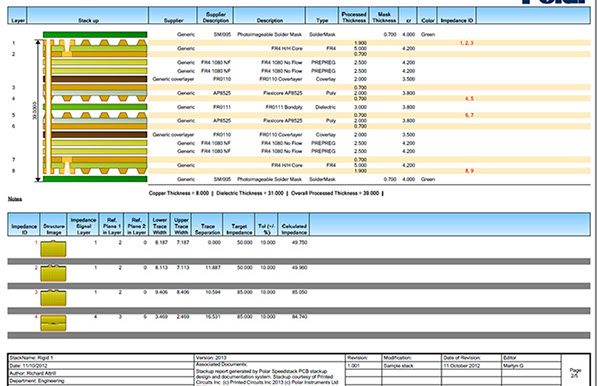

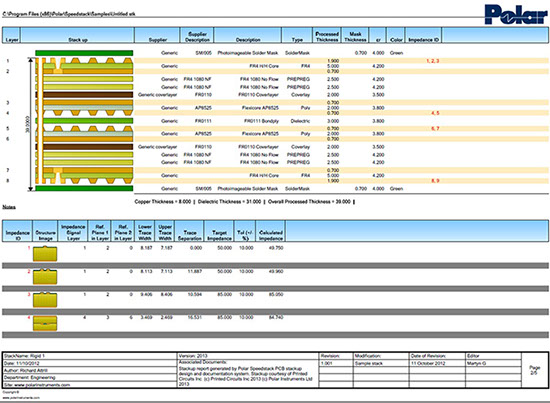

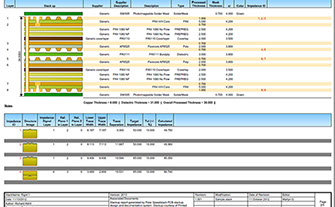

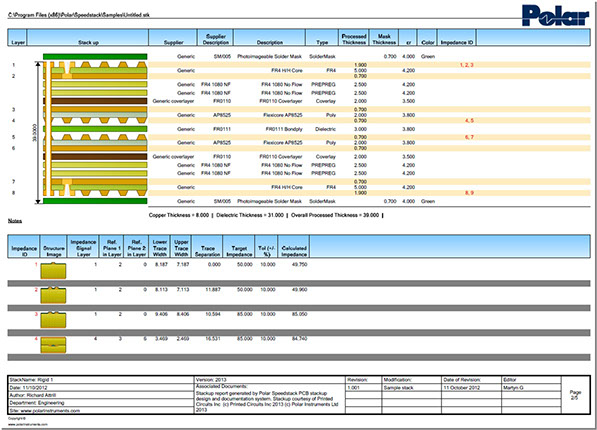

Speedstack Beispiel-Ausdruck

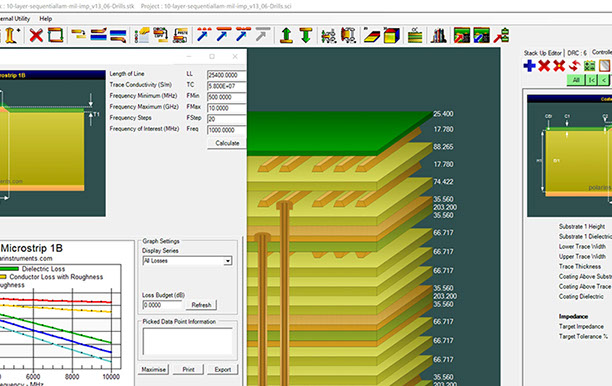

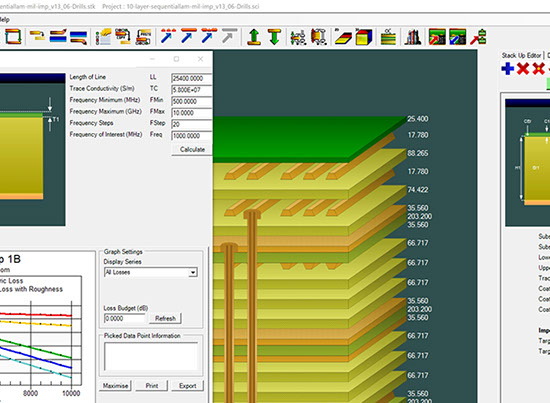

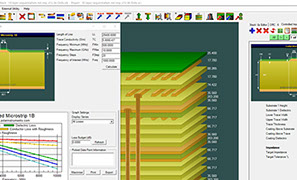

Speedstack Gesamtansicht

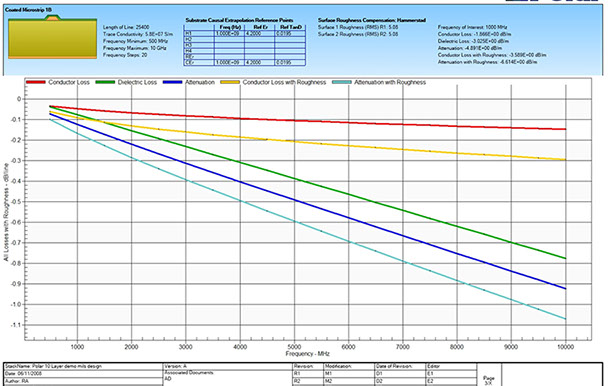

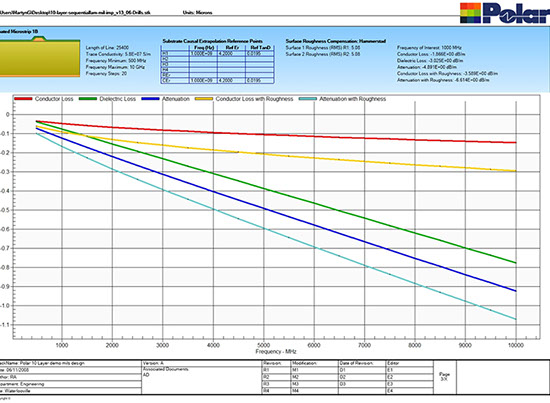

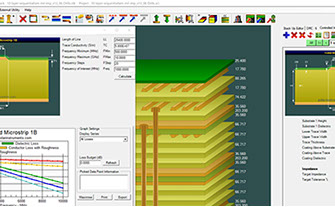

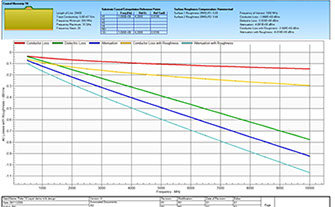

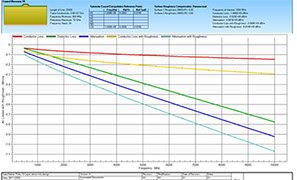

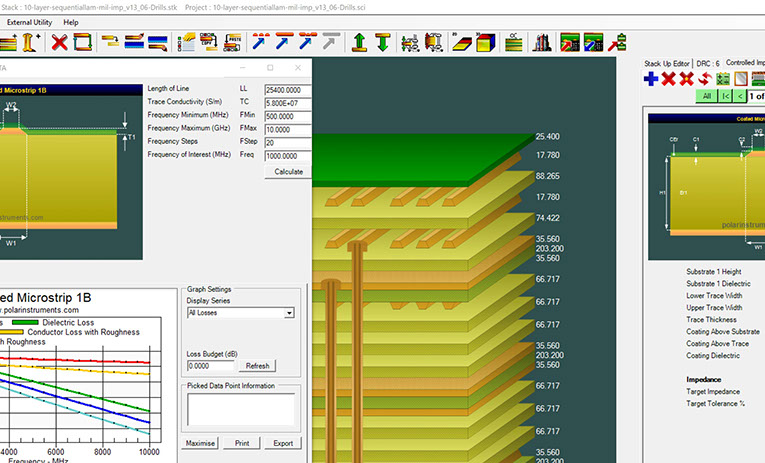

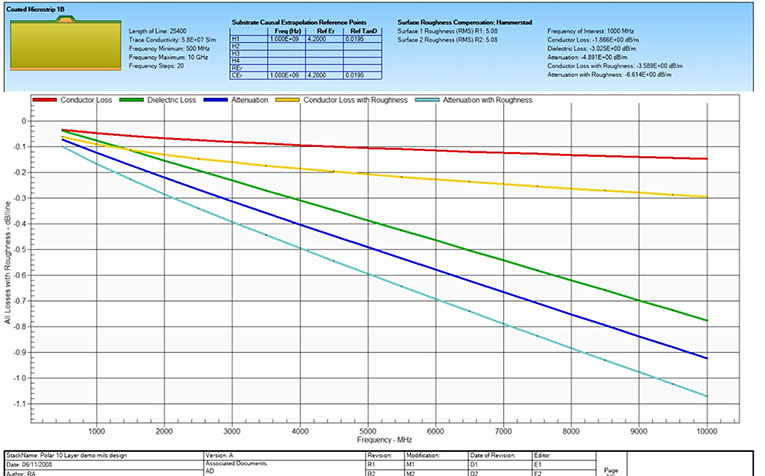

Speedstack Dämpfungsberechnung

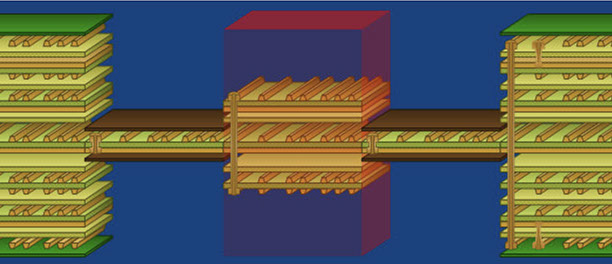

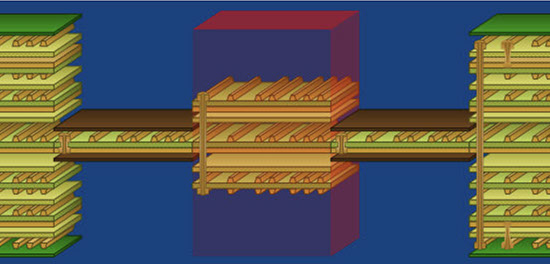

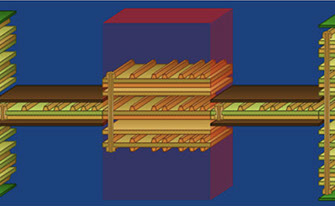

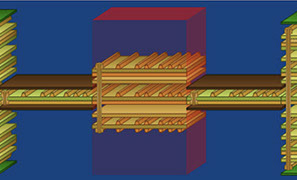

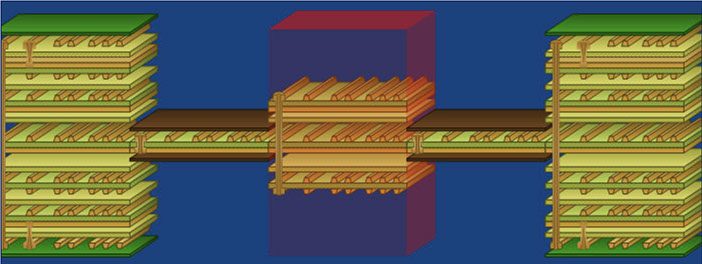

Speedstack Starrflex-Aufbau

Warum sollten Sie Lagenaufbauten mit Speedstack erstellen?

Leiterplattenhersteller stellen fest, dass Speedstack die Zeit zur Erstellung eines Lagenaufbaus erheblich reduziert im Vergleich zu traditionellen Methoden. Entwickler schätzen Speedstack aufgrund der professionellen und unmissverständlichen Dokumentation zum Informationsaustausch mit dem Leiterplattenhersteller.

Wie unterstützt Sie Speedstack?

Speedstack ermöglicht Ihnen die Erstellung von kompletten "Live"-Lagenaufbauten inklusive Impedanzinformationen - entweder aus einer allgemeinen Materialdatenbank oder von einer eigenen Bibliothek bestehend aus Prepregs, Kernen und Lötstopmasken. Speedstack verwendet die Ausgangsdaten (Dickenvorgabe, Lagenzahl, Impedanzanforderung) und erzeugt daraus automatisch einen Lagenaufbau entsprechend den Vorgaben - Kosten, Enddicke, Lieferzeit etc.

Wie erfolgt der Lagenaufbau?

Mit Speedstack haben Sie jederzeit die volle Kontrolle über den Lagenaufbau - Sie können den Aufbau so eng oder weit spezifizieren, wie Sie wünschen. Für Standardaufbauten geben Sie einfach die gewünschte Enddicke und Lagenzahl sowie die Impedanzanforderungen (falls vorhanden) an und lassen Speedstack die zur Erzielung der erforderlichen Lagenabstände benötigten Materialien automatisch einfügen. Sie können - wenn gewünscht - auch eine bevorzugte Kerndicke angeben. Als erfahrener Anwender können Sie den Aufbau auch völlig manuell erstellen. Die Autostack-Funktion bietet Ihnen maximale Zeitersparnis - hier die Funktionsweise: Das Autostack-Modul nimmt zunächst die Gesamtdicke und ordnet nominale Lagenabstände zu. Der Feinabgleich der Lagenabstände erfolgt dann während der Impedanz-Zielsuche. Über eine "Ampelanzeige" werden jene Bereiche gekennzeichnet, welche nahe der geforderten Spezifikation liegen. Sind Sie mit dem vorliegenden Aufbau einverstanden, erstellt Speedstack eine Auswahl an Lagenaufbauten - typisch 10 - 20, geordnet nach Lieferzeit, Kosten oder Enddicke. Jeder Lagenaufbau wird virtuell 10 000-fach nach der Monte-Carlo-Analyse aufgebaut, um eine maximale Fertigungsausbeute zu erzielen. Wählen Sie den bevorzugten Lagenaufbau und Speedstack erledigt eine letzte Feinanpassung der Leiterbreiten für maximale Impedanzgenauigkeit. Der erstellte Lagenaufbau kann dann per E-Mail an die Hersteller gesandt werden, welche die Datei mit dem Speedstack Viewer öffnen. Alternativ kann ein professioneller Ausdruck zur Dokumentation in Papierform erzeugt werden.

Speedstack im Vergleich zu konventionellen Lagenaufbaumethoden?

Durch die Verwendung von konventionellen Lagenaufbaumethoden riskieren Sie kostspielige Missverständnisse beim Austausch der Daten zwischen Layouter und Leiterplattenhersteller. Im günstigsten Fall ist die Leiterplatte geringfügig außerhalb der Spezifikation - im schlechtesten Fall ist dies zu dick für einen Leiterplatten-Stecker oder die Impedanzvorgaben werden nicht eingehalten. In diesem Fall ist eine Neufertigung unumgänglich.

Die Vorteile von Speedstack:

Die Erstellung des Lagenaufbaus nimmt nur mehr einen Bruchteil der bisher benötigten Zeit in Anspruch. Sie erstellen eine professionelle, umfassende Dokumentation - vollautomatisch. Sie vermeiden Kommunikationsprobleme durch eine klare und unmissverständliche Beschreibung des Lagenaufbaus. Wenn Sie mehr über Speedstack erfahren möchten, so kontaktieren Sie uns bitte. Lernen Sie Speedstack selbst über eine Demoversion oder eine kurze Präsentation über das Internet kennen. Klicken Sie hier für eine Anforderung einer Demoversion.

Speedstack Lagenaufbausoftware inklusive Materialdatenbank und Design Rule Checks. (ohne Impedanzberechnung)

Speedstack PCB Bündellösung enthält Speedstack Lagenaufbaumodul und Si8000m Impedanzberechnung (mehr)

Speedstack Si Bündellösung enthält Speedstack Lagenaufbaumodul und Si9000e Impedanzberechnung

Speedstack bietet:

- Automatischer Lagenaufbaugenerator

- Rasche Erstellung von Lagenaufbauten

- Klare und umfassende Dokumentation

- Basismaterial-Bibliotheken

- IPC Materialbezeichnungen

- Ausgabe von CITS Impedanzprogrammen

- Impedanz-Zielsuche

- konfigurierbare Ansicht und Ausdruck

- Stacked Vias

- Stacked Mikrovias

- verbesserte Dickenberechnung

- verbesserter Design Rule Check

- Berechnung des Harzverfüllungsgrades

- Vorgabe einer Solldicke

- Schnittstelle zu Si8000m und Si9000e

- Ausgabe auch als *.jpg

- Speichern der Impedanz-Daten als .sci Datei

- Dateiausgabe im Gerber, DXF, ASCII Format

- Enddicken-Kompensation

- Support für Microvias

- Import von Materialdatenbanken

- Unterstützung zusätzlicher Materialtypen

Sparen Sie Zeit

Die Steuerung und Dokumentation von komplexen Lagenaufbauten nimmt immer mehr Zeit von Layoutern und Arbeitsvorbereitern in Anspruch. Informationen zum Lagenaufbau können mit Speedstack sehr einfach in einem Standardformat weitergegeben werden.

Für Leiterplattenhersteller:

Dokumentieren Sie Ihre Lagenaufbauten rasch und professionell. Teilen Sie Materialtypen und wichtige Laugenaufbauinformation Ihren Mitarbeitern und Kunden mit.

NEU: Durch die automatische Generierung von CITS *.cif Testdateien aus dem Lagenaufbau sparen Sie Zeit und vermeiden Fehlerquellen.

Für Layout-Designer:

Verschaffen Sie sich einen raschen Überblick über den Lagenaufbau und tauschen Sie diese Daten mit Ihrem bevorzugten Leiterplattenhersteller aus.

Für CAD-Abteilungsleiter:

Sie arbeiten mit mehreren Leiterplattenherstellern zusammen? Oder Sie möchten einen fehlerfreien Übergang von der Prototypenfertigung in die Großserie? Speedstack enthält sämtliche relevanten Lagenaufbauinformationen in einem einfach zu verwaltenden Format.

Für Schaltungsentwickler:

Zählt Leiterplattenfertigung für Sie zu "schwarzer Magie"? Speedstack unterstützt Sie bei der Definition Ihrer Anforderungen an den Leiterplattenhersteller (oder Kunden). Somit wird sichergestellt, dass Sie kostengünstiger Leiterplatten nach Ihren Spezifikationen erhalten.

Für Einkäufer und Händler:

Haben Sie jemals Leiterplatten erhalten, welche äußerlich in Ordnung schienen, bei näherer Untersuchung jedoch Fehler in Form von vertauschten Lagen oder inkorrekte Impedanzwerte aufwiesen? Verhindern Sie diese Probleme, indem Sie bereits in der Entwicklung die Lagenaufbauten mit Speedstack dokumentieren. Der Datenaustausch im Speedstack-Format sorgt für reibungslose Kommunikation zwischen Entwickler und Leiterplattenhersteller.

Kundenspezifische Ausdrucke:

Der neue Report Writer bietet kundenspezifische Dokumentation nach Maß.

Klare, umfassende Dokumentation:

Erstellen und dokumentieren Sie Lagenaufbau-Informationen in einem klaren und konsistenten Format. Die Materialauswahl und der Lagenaufbau kann einfach ausgedruckt oder in Dateiform zwischen Leiterplatten-Designer und Leiterplattenhersteller ausgetauscht werden.

Design Rule Check:

Echtzeit-Design Rule Checks zeigen fehlerhafte Materialwahl, Kupfer-Unsymmetrie, RCC-Folien auf Innenlagen und weitere Designparameter.

Ihre Materialdatenbank:

Leiterplattenhersteller können eine eigene Datenbank mit häufig verwendeten Standardmaterialien und Lagerware anlegen. Informationen über Preise und Material-eigenschaften können hinterlegt werden. Diese Informationen stehen den Designer zur Verfügung, um die richtige Materialauswahl basierend auf den Kosten/Lieferzeit und Eigenschaften treffen zu können.

Eine umfangreiche Materialdatenbank aller namhaften Hersteller steht hier zum Download bereit.

Systemanforderungen

Eine Übersicht über die PC-Systemanforderungen finden Sie unter AP605

Für weitere Fragen oder eine Demoversion der Speedstack kontaktieren Sie uns unter germany@polarinstruments.eu oder Tel. +43 7666 20041-0

Polar instruments GmbH

Aichereben 16

4865 Nussdorf am Attersee

Austria

+43 7666 20041-0

Fax +43 7666 20041-20

Polar Instruments (Asia Pacific) Pte Ltd

Interlocal Centre, #07-23

100G, Pasir Panjang Road,

Singapore 118523

+65 6873 7470 / +65 6873 7470

Fax +65 6872 7471

mail@polarinstruments.asia

www.polarinstruments.asia